Modeling the VTA Machine Learning Accelerator in ACADL for Performance Predictions

Bearbeitet von J. Gietz.

Bachelor’s Thesis / Master’s Thesis / Student Research Project

Abstract

Abstract modeling of HW/SW systems is a relatively new research topic. This technique aims to capture only the essential parameters of software and hardware that influence their timing behavior.

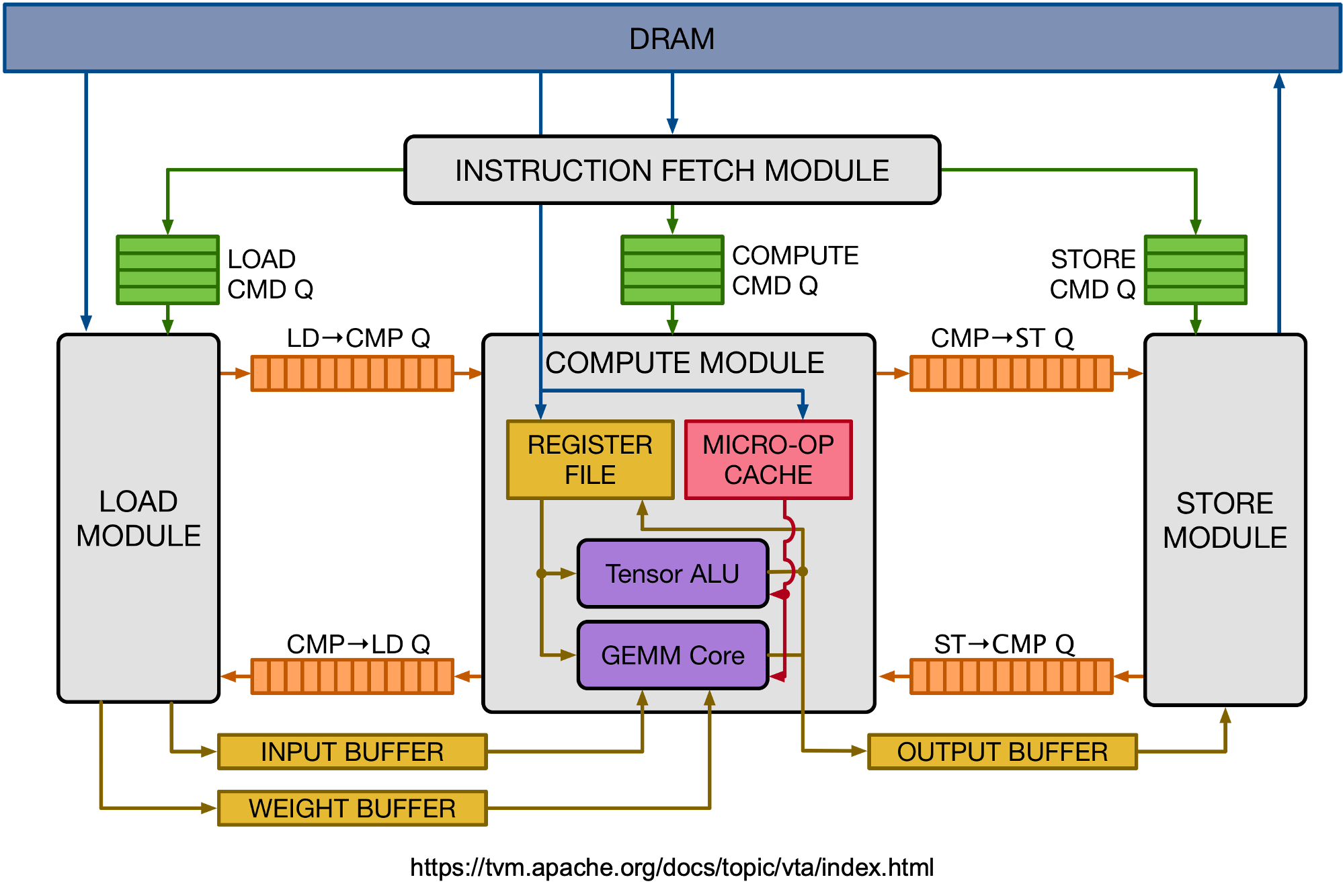

This student project’s goal is to model the VTA Machine Learning Accelerator using the Python-based Abstract Computer Architecture Description Language (ACADL) and use different methods for runtime/performance prediction and compare those against the cycle-accurate hardware model.

Block diagram of the VTA Architecture (source)

References

Requirements

- Python

- Successfully atteded the lecture “Grundlagen der Rechnerarchitektur” and/or “Parallele Rechnerarchitekturen” (optional)

- Linux (optional)